| |

|

Главная » Мануалы 1 ... 37 38 39 40 41 42 43 !7.5. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ 7.5а. Логический элемент И Логический элемент И имеет выходной сигнал, определяемый логической функцией И его входных сигналов. Так, если все входы логического элемента имеют состояние логической 1, то и его выход имеет состояние логической 1. В табл. 7.3(a) приведены стандартное графическое изображение, логическое выражение и таблица истинности двухвходового логического элемента И. Как видно из таблицы истинности, для получения на выходе У логической 1 необходимо наличие логической 1 как на входе А, так и на входе В. Логическое выражение представляет собой другую форму записи таблицы истинности. Выход Y равен логической 1, когда входы А и В равны логической 1. Хотя в нашем примере рассмотрен двухвходовый логический элемент И, помимо микросхем с двухвходовыми элементами И промышленностью выпускаются микросхемы, содержащие четыр'ех- и вось-мивходовые логические элементы И. 7.56. Логический элемент И-НЕ Логический элемент И-НЕ можно рассматривать как элемент реализующий логическую функцию И-НЕ. Если на выход логического элемента И, рассмотренного выше, поставить инвертор, выполняющий логическую функцию НЕ, то получится логический элемент И-НЕ. Если все входы элемента имеют состояние логической 1, то его выход имеет состояние логического О. В табл. 7.3(6) приведены стандартное графическое изображение логическое выражение и таблица истинности двухвходового логического элемента И-НЕ. Обратим внимание на кружок на выходе логического элемента, черту над правой частью логического выражения и на выход таблицы истинности. Такая символика отражает реализацию функции НЕ по отношению к логическому элементу И. Выпускаются микросхемы, содержащие двух-, трех- четырех- и восьмивходовые логические элементы И-НЕ. 7.5в. Логический элемент ИЛИ Логический элемент ИЛИ имеет выходной сигнал, определяемый логической функцией ИЛИ его входных сигналов. Так, если хотя бы один из входов логического элемента имеет состояние логической 1, то и его выход имеет состояние логической 1. В табл. 7.3(b) представлены стандартное графическое изображение, логическое выражение и таблица истинности двухвходо- Функция Стандартное графическое изображение Логическое выражение Таблица истинности &) И €) И-НЕ в) ИЛИ г) ИЛИ-НЕ д) ИСКЛЮЧАЮЩЕЕ ИЛИ е) ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ /I-В- У = А-В Y = A-B , Y = AB + AB Y = A-B + AB \ = A@B ж) Инвертор (HE) Y -

Таблица 7.3. Базовые логические элементы функция Стандартное графическое изображение Логическое выражение Таблица истинности 3) И-ИЛИ и) И-ИЛИ-НЕ /?-В-

ВОГО логического элемента ИЛИ. Из таблицы истинности видно, что если на входах А или В присутствуют логические 1, то и выход элемента имеет логическую 1. Логическое выражение, как и выше, подтверждает таблицу истинности: выход У равен логической 1, когда на входе А или входе В присутствует логическая 1. Выпускаются микросхемы, содержащие двух-, трех-, четырех- и восьмивходовые логические элементы ИЛИ. 7.5г. Логический элемент ИЛИ-НЕ Логический элемент ИЛИ-НЕ эквивалентен логическому элементу ИЛИ, к выходу которого подключен инвертор, реализующий функцию НЕ. Если хотя бы один из входов логического элемента имеет состояние логической 1, то его выход имеет состояние логического 0. В табл. 7.3 (г) приведены стандартное графическое изображение, логическое выражение и таблица истинности для двухвходового логического элемента ИЛИ-НЕ. Обратим внимание на кружок на выходе логического элемента, черту над правой частью логического выражения и на выход таблицы истинности. Таблица истинности этого логического элемента является полной инверсией таблицы истинности логического элемента ИЛИ. Микросхемы, выпускаемые промышленностью, содержат двух-, трех-, четырех- или восьмивходовые логические элементы ИЛИ-НЕ. 7.5д. Логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ Логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ имеет выходной сигнал, определяемый логической функцией ИСКЛЮЧАЮЩЕЕ ИЛИ его входных сигналов. Если только один из входов логического элемента имеет состояние логической 1, то и его выход имеет состояние логической 1. Любая другая комбинация состояний входов логического элемента приводит к появлению на его выходе состояния логического 0. В табл. 7.3 (д) представлены стандартное графическое изображение, логическое выражение и таблица истинности двухвходового логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Символ ф в логическом выражении обозначает функцию ИСКЛЮЧАЮЩЕЕ ИЛИ. Понимание взаимосвязи между логическими функциями ИЛИ и ИСКЛЮЧАЮЩЕЕ ИЛИ может помочь читателю осмыслить происхождение названия ИСКЛЮЧАЮЩЕЕ ИЛИ. Логическая функция ИЛИ, полное наименование которой ВКЛЮЧАЮЩЕЕ ИЛИ, означает появление на выходе элемента состояния логической 1. Любой вход (один или несколько) является включающим, поскольку в этом случае охватываются все комбинации, яри которых вход(ы) находится в состоянии логической 1. И наоборот, логическая функция ИСКЛЮЧАЮЩЕЕ ИЛИ означает появление на выходе логической 1 тогда и только тогда, когда лишь один вход имеет состояние логической 1 и исключается вариант, при котором больше чем один вход находится в состоянии логической 1 (см. таблицу истинности для логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ). Этим и объясняется происхождение названия данной логической функции. Две интересные логические функции могут быть получены с помощью логической функции ИСКЛЮЧАЮЩЕЕ ИЛИ. Из таблицы истинности можно видеть, что выход У находится в состоянии логического О при одинаковом состоянии обоих входов. Таким образом, логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ можно использовать для реализации логической функции сравнения. Кроме тОго, можно заметить, что если вход В находится в состоянии логического О, то состояние выхода Y соответствует состоянию входа А. И наоборот, если вход В имеет состояние логической 1, состояние выхода Y соответствует инверсии состояния входа А. Вследствие этого существует возможность реализовать функцию инверсия/отсутствие инверсии программным способом. Выпускаемые микросхемы содержат двухвходовые логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ. 7.5е. Логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ Логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ можно рассматривать как элемент, реализующий логическую функцию ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ. Состояние его выхода представляет инверсию состояния выхода логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Выход Y находится в состоянии логического О тогда и только тогда, когда лишь один из входов А или В имеет состояние логической 1. Во всех других случаях выход элемента имеет состояние логической 1. В табл. 7.3(е'к представлены стандартное графическое изображение, логическое выражение и таблица истинности двухвходового логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ. Микросхемы, выпускаемые промышленностью, содержат двухвходовые логические элементы ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ. 7.5ж. Логический элемент НЕ (инвертор) Логический элемент НЕ имеет выходной сигнал, представляющий собой инверсию входного сигнала. Так, если вход инвертора находится в состоянии логической 1, то его выход имеет состояние логического 0. И наоборот, если вход инвертора имеет состояние логического О, то его выход имеет состояние логической 1. В табл. 7.3 (ж) приведены стандартное графическое изображение, логическое выражение и таблица истинности инвертора. Заметим, что функция инверсии может быть реализована и с помощью других логических функций НЕ (И-НЕ, ИЛИ-НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ), а не только с помощью инвертора. Для каждого из упомянутых логических элементов читатель может по соответствующей таблице истинности (табл. 7.3) определить, что нужно подать на неиспользуемые входы. 7.5з. Логический элемент И-ИЛИ Функция И-ИЛИ мало отличается от рассмотренных выще функций. Две логические функции реализуются с помощью логического элемента И-ИЛИ. Вначале реализуется логическая функция И, а затем ИЛИ. В табл. 7.3 (з) показаны стандартное графическое изображение, логическое выражение и таблица истинности двух двухвходовых логических элементов. Выход Y имеет логическую 1, если в точке Е и (или) точке F имеется логическая 1. В свою очередь точка Е имеет логическую 1, если входы С и D имеют логическую 1. Следовательно, выход У имеет состояние логической 1, если входы А и В имеют состояние логических 1 или входы С к D имеют состояние логических 1. 7.5и. Логический элемент И-ИЛИ-НЕ Три логические функции реализуются в логическом элементе И-ИЛИ-НЕ последовательно. Вначале реализуется функция И для группы входов. Затем выполняется функция ИЛИ для результатов реализации каждой функции И и, наконец, выполняется функция НЕ, т. е. производится инверсия окончательного результата. В табл. 7.3 (и) представлены стандартное графическое изображение, логическое выражение и таблица истинности логического элемента И-ИЛИ-НЕ с двумя группами двухвходовых элементов И. Из таблицы истинности видно, что для получения на выходе У состояния логического О необходимо иметь состояние логической 1 либо на входах А к В, либо на входах С и D. Читатель может заметить, что функция И-ИЛИ-НЕ представляет собой инверсию рассмотренной выше функции И-ИЛИ. Промышленностью выпускаются микросхемы, которые содержат логические элементы И-ИЛИ-НЕ, имеющие группы из двух, трех, четырех входовых элементов И с числом таких групп две или четыре. Пример 7.1. Проектирование дешифратора. Требуется разработать схему дешифратора, входные сигналы которого 10, 11, 12 и выходные сигналы 00, 01, 02, 03 которого удовлетворяют таблице истинности, представленной на рис. 7.8. Ю-ff .f2

-00 -01 -02 03 а

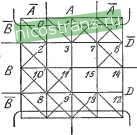

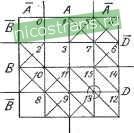

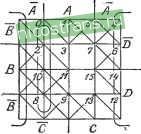

Рис. 7.8. Дешифратор для примера 7.1. Блок-схема (о); таблица истинности (б). Решение. а) Отобразим, во-первых, выходной сигнал 00 на карте Мэхани (см. [4]). б) Соединим все возможные входы на карте следующим образом:

в) Преобразуем результаты и запишем выражение, содержащее минимальное число произведений: 00 = 5 -Ь (АС АС). г) 00 = В Л е С. Повторим этапы а - в для выходных сигналов 01, 02, 03.

В а 01=0+ BC + A@J3-C .02=/! ВС

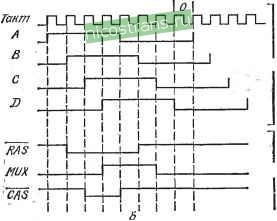

в у =0-ЙЗ -Of load 3>г> ~У-03 Pop 02pu3f7 -00 Zero Рис. 7.9. Решение примера 7.1. Пример 7.2. Получение сигналов синхронизации заданного вида. Задана выходная последовательность сигналов регистра Джонсона, представленная *RAS *мах *CAS а \1\3 \ 7\f5\fJf\l2\8  -Выход Рис 7.10. Постановка задачи для примера 7,2. Блок-схема (о); временная диаграмма (б). Схема дешифратора в результате примет вид, представленный на рис. 7.9. на рис. 7.10. Требуется получить следующие сигналы синхронизации: ras, mux, cas. Решение. а) На основании временной диаграммы составим таблицу истинности. Такт D С В А б) Отобразим состояние каждого выхода, представленного в таблице и& тинности    в) Запишем логическое выражение для каждого выхода! MUX ==C-D. CAS = A + C, или CAS = Л С. г) По логическому выражению синтезируем схему, которая приведена на рис. 7.П. -RAS -MUX- -CAS А(1) В(2) СО-) Ш8) 77рео5разо-ватемб кода >0 Рис. 7.11. Схемное решение примера 7.2. Рис. 7.12. Преобразователь двоичного кода в десятичный для примера 7.3. Пример 7.3. Преобразователь двоичного кода в десятичный. Требуется разработать схему, которая преобразует двоичный взвешенный код (1248) в десятичный код в соответствии с рис. 7.12. Решение. а) Составим таблицу истинности, отражающую все возможные комбинации входных и выходных сигналов.

б) Отобразим каждый выходной сигнал от О до 9 на карте Мэхани. в) Используя логическое выражение, синтезируем схему, реализующую каждую логическую функцию. Решение представлено на рис. 7.13. 1 ... 37 38 39 40 41 42 43 |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||