| |

|

Главная » Мануалы 1 2 3 4 5 6 7 8 ... 22 Рис. 1.17. Зависимость числа подряд ошибочных слов в одном звуковом канале иа выходе декодера CIRC от длины выпадений для различных стратегий исправления ошибок во второй ступени декодирования: а - длина выпадений меньше 65 блоков, б - длина выпадений больше 65 блоков ОТ исправляющей способности Д2, пока iV621. При больших длинах выпадений данная зависимость выражена слабо. Пересечение кривых с осью абсцисс определяет длину полностью исправляемых выпадений, которая в зависимости от стратегии декодирования в Ц2 равна 3, 8, И и 15 блокам. При относительно малом интервале межблочного перемежения (четыре блока) большой диапазон выпадений, исправляемых с помощью линейной интерполяции, обеспечивается в коде CIRC благодаря разумному сочетанию с внутриблочной перестановкой символов. Очень важной характеристикой является зависимость скорости нарастания числа ошибочных слов (о=1) от длины выпадения. На кривых четко видны точки, где скорость нарастания становится равной 6 слов/блок, а именно при N5 = 8, 13, 15 и 21 блокам. Если учесть, что в блоке данных всего 12 слов (шесть слов левого и шесть слов правого каналов), то, следовательно, в этих точках исправляющая способность декодера по приращениям становится равной единице. Это значит, что когда длина выпадения увеличивается на один блок, число неисправленных слов увеличивается на 6 (ни одно слово не исправляется!). При длине выпадений свыше 21 блока влияние стратегий декодирования становится очень малым, но а монотонно растет. При iV6>51 блока рост числа одиночных ошибочных слов прекращается и начинают возникать выпадения ошибочных слов длиной по 2, 3, 4 и 5 слов подряд ((т=2, 3, 4, 5). При выпадениях свыше 72 блоков на выходе декодера начинают возникать однократные выпадения ошибочных слов длиной 10, 16, 22 и более слов подряд, которые никакой интерполяцией исправить нельзя. Таким образом, по исправлении длинных выпадений можно выделить три диапазона: диапазон полного исправления выпадений длиной 3, 8, И и 15 блоков; диапазон исправлений выпадений с помощью линейной интерполяции - 49(51) блоков и диапазон выпадений, исправляемых с помощью интерполяции нулевого порядка, - 72(74) блока. При расчете длительности исправляемых выпадений в Д1 необходимо учесть, что длина всего блока в коде CIRC равна 588 канальных бит, длина информационного символа - 14 канальных бит, а промежуток между ними - три канальных бита. При блочной частоте 7,35 кГц длительность информационного символа 3,24 мкс, а промежуток между ними 0,69 мкс. При таких данных в Д1 полностью исправляется выпадение до 8 символов, которое соответствует длительности 30,5 мкс. Максимально допустимач частота повторения таких пакетов и выпадений с защитным интервалом второго блока - 3675 Гц. При определении максималь- яо допустимых временных выпадений, которые исправляются в М2, достаточно приведенные выше длины в блоках умножить на длительность блока 136 мкс. В рассмотренной суперстратегии декодирования фирмы Sony .обеспечивается возможность исправления в первой ступени декодирования выпадений длительностью до 15,2 мкс с защитным ин-гервалом 272 мкс, а во второй ступени декодирования- 1,09 мс с защитным интервалом 15,9 мс и линейной интерполяцией оши--бочных слов при длительности выпадений до 6,7 мс с защитным интервалом 21,5 мс. Как видно, это далеко не предельные возможности кода CIRC. Структурные схемы кодера и декодера. В связи с тем, что в оде CIRC код Сг является несистематическим, а С] - систематическим, кодирование целесообразно проводить на основе проверочных матриц, а не использовать порождающие многочлены. При таком подходе проверочные символы в обеих ступенях кодирования могут быть вычислены путем векторного перемножения матриц; для кода Сг (1.34)

(1.35) где a м b - полусиндромы ошибок: 11 27 31 == 2 a* + 2 a* и 6 = 2 i=--0 1=16 1=0 - проверочные символы, О^/З. Приведенные расчетные формулы упрощают построение кодера в виде специализированного вычислительного устройства, содержащего оперативную память ОЗУ для выполнения операций перемежения и перестановки символов при кодировании, постоян-шого запоминающего устройства ПЗУ для хранения констант и процессора для адресации данных и выполнения арифметических .операций в поле Галуа. В структурную схему такого кодера входит ОЗУ емкостью 2КХ8 бит, блок адресации БА и арифметический блок АБ (рис. 1.18). Микропрограммный счетчик МПС определяет адреса всех ПЗУ, содержащих микропрограммы, с которыми он связан 8-разрядной шиной. В блоке адресации выполняется перемежение данных на принципе динамического распределения памяти, при котором за каж-46 Счетчик 0лопов Блок адресации 1 Счетчиц Блоков Ь1числе,1ип ПС ОЗУ вычислений. Л ПЗУ

Рис. 1,18. Структурная схема кодера CIRC ДЫМ символом блока данных (информационным и проверочным) закрепляется определенная зона ОЗУ. Расположение зон одновременно смещается с каждым новым блоком. Для этого в БА подается блочная частота и введен счетчик блоков. Вычисленные адреса для записи в ОЗУ входных данных и проверочных символов, а также для их считывания подаются в ОЗУ по 11-разрядной шине адресации. В арифметическом блоке (АБ) производятся вычисления проверочных символов в поле Галуа. Сначала определяются полусиндромы ПС, которые хранятся в буферном регистре R\G. Операция умножения матрицы М на вектор-столбец из полусиндромов выполняется с помощью логарифматора Л, сумматора по модулю 255, антилогарифматора АЛ и сумматора по модулю 2. Умножение элементов поля Галуа производится в показательной форме с использованием ПЗУ, где хранятся показатели степеней. Поступление данных и выдача их осуществляются по одной 8-разрядной шине данных. Синхронизация работы кодера осуществляется от кварцевого генератора с частотой 4,2336 МГц. Делением на 18 формируется частота следования символов на выходе кодера 235,2 кГц. Формирование символов на входе кодера (от АЦП) производится с частотой 176,4 кГц (коэффициент деления - 24). Частота дискретизации 44,1 кГц и частота следования блоков 7,35 кГц образуются при делении на 96 и 192 соответственно. За время одного блока 136 мкс число обращений к ОЗУ равно 116, в том числе запись входных символов - 24, считывание символов ~ 32, считывание данных для вычисления полусиндромов в коде Сг-24, в коде Cj-28 и запись проверочных символов - 8. Операция умножения вектора полусиндрома на матрицу выполняется за 24 шага. Таким образом, вся микропрограмма занимает 160-170 шагов. В структурную схему декодера на рис. 1.19 входят оперативное ЗУ, арифметический блок АБ, блок адресации БА и программное устройство ПУ. Блоки связаны между собой многоразрядными шинами данных и адресными шинами. Эта общая схема мало отличается от структурной схемы кодера. Поток цифровых данных от демодулятора канального кода поступает на шину данных ДВ. Часть объема ОЗУ используется как буферная память, необходимая для сопряжения неравномерной скорости считывания информации с компакт-диска с кварцевой частотой ге- £лон номыцтацаи ffm считывающего устройства Е

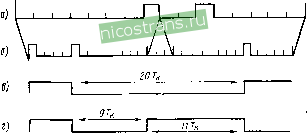

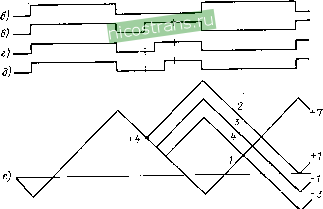

I I I Адресная III -5 у *: <>: Интерполятор Г -J u Еипхронизатор Рис. 1.19. Структурная схема декодера CIRC 48 -ИпВ 1 0 3INF о-НКЛ ® GJ/C2 Азт ПЗУ ?+ *! \Ы\ и BINS Рис. 1.20. Структурная схема арифметического блока нератора синхросигналов декодера. Другая часть ОЗУ используется для перемежения символов при декодировании, а третья- для хранения флагов стертых символов. Адрес обращения с ОЗУ определяется адресным генератором в соответствии с заданной программой. Адрес поступает в ОЗУ по -разрядной шине, что определяется емкостью ОЗУ. В адресный блок входят три генератора, осуществляющие обмен информацией с ОЗУ по программе, адресацию данных с декодера EFM и считывание данных после декодирования в интерполяторе. Управление генераторами осуществляется блоком приоритетов. В арифметическом блоке производится вычисление синдромов ошибок, идентификация ошибок в блоке данных, определение локаторов ошибок и расчет ошибок и стираний. Именно в этом блоке задается стратегия декодирования. Управление арифметическим блоком осуществляется от микропрограммного счетчика и ПЗУ микрокоманд. Более детальная структурная схема АБ, в котором исправляются одиночные и двойные ошибки в соответствии с формулами, приведенными выше, представлена на рис. 1.20. В этой схеме производится вычисление коэффициентов А, В и С, определяются локаторы ошибок i и / и значения ошибок ег и ej. Результаты промежуточных вычислений хранятся в регистрах RG. 1.3. КАНАЛЬНАЯ МОДУЛЯЦИЯ СПОСОБОМ EFM Назначение канальной модуляции. Сформированный цифровой сигнал в соответствии с правилами, изложенными в § 1.2 и 1.3, при воспроизведении не во всех случаях может быть восстановлен из-за Мешающих факторов. Так, когда все 16 бит, выражающих численное значение сигнала, являются нулями, то на дорожке длительное время отсутствуют питы (углубления на дорожке ком- пакт-диска, соответствующие наличию импульса кодового обозначения информации) и их отсутствие может привести к сбою слежения за дорожкой или нарушению фокусировки лазера. Одновременно в сигнал следует ввести синхроимпульсы, необходимые для стандартизации измерения временных интервалов, для чего необходимо попеременное прохождение определенного числа О и 1. Поэтому цифровой сигнал следует преобразовывать в форму так, чтобы обеспечивались стабильная запись и воспроизведение сигнала в заданной полосе частот, т. е. необходимо согласовывать полосу частот сигнала с полосой пропускания канала записи-воспроизведения, определяемой свойствами оптической системы воспроизведения. С уменьшением длины пита уменьшается амплитуда полезного сигнала, так как амплитудно-частотная характеристика воспроизведения имеет ограничение по частоте. Поэтому существует минимально допустимый временной интервал между переходами в записываемом сигнале, ограниченный некоторым максимальным значением из-за опасности образования больших участков дорожки записи без пит. Механические помехи на диске вносят некоторые изменения в характер огибающей воспроизведения питов. Последние носят характер низкочастотной помехи, синхронизованной с частотой вращения диска. Несмотря на то, что спектр помехи смещен относительно спектра основного сигнала и легко устраняется, низкочастотная составляющая вызывает принудительную модуляцию основного сигнала и нарушает работу систем авторегулирования. Поэтому необходима такая модуляция, при которой длительность отсутствия импульсов не превышает определенного значения, а комбинация импульсов вызывает подавление низкочастотной составляющей основного сигнала, влияющей на работу систем авторегулирования. Основные правила способа EFM и формат записи данных. Способ EFM относится к числу групповых способов канальной модуляции. Исходный цифровой ЗС разбивается на группы (называемые символами) длительностью по восемь цифровых бит, и каждый такой символ на стандартизованной табл. П1.3 (приложение 1) заменяется соответствующей комбинацией из 14 канальных бит. Поэтому способ получил название EFM (Eight to For-teen Modulation). Все 256 цифровых символов, подлежащих модуляции, приведены в приложении 1 в колонке 2 (двоичное представление), колонке 1 (десятичное представление) и колонке 4 (шестнадцате-ричное представление). Соответствующие канальные символы приведены в колонке 3 (двоичное представление) и колонке 5 (шестнадцатеричное представление). При этом значения канальных символов приведены в дифференциальном виде, когда единицами обозначаются те канальные биты, на которых должна про- изводиться смена полярности канального сигнала на противоположную. При последовательном считывании канального сигнала между канальными символами вставляется группа из трех бит, называемых переходными. Один из них может (но не обязательно) иметь значение 1. Правила выбора переходного бита будут рассмотрены ниже. Способ EFM при разумном выборе переходного бита позволяет получить минимальную длительность канального сигнала, составляющую три канальных бита или 1,41 цифровых бит, что в 1,41 раза снижает максимальную частоту спектра записываемого сигнала, и максимальную длительность канального сигнала, равную И канальным битам, что позволяет существенно уменьшить мощность низкочастотных составляющих спектра записываемого сигнала. Дальнейшее уменьшение низкочастотной части спектра достигается индивидуальным выбором варианта перехода между каждой парой канальных символов. При записи данные организуются в блоки (рис. 1.21) длиной 588 канальных бит, включающие синхрогруппу из 24 канальных бит, символ управления и отображения информации - 14 канальных бит, 24 символа данных по 14 канальных бит каждый, 34 группы переходных бит по три канальных бита каждая. Поскольку каждые восемь цифровых бит заменяются на 17 канальных бит, из которых 14 выбирают по правилам приложения 1, а три оставшихся определяют по отдельному правилу, то тактовая частота следования канальных бит составляет 17/8 тактовой частоты следования цифровых бит. Соответственно длительность , I блок (see канальных Sum) п -ЦоВаВочпые Виты для согласования и подаВлемия НЧ составляющей. 24 \Н И Н 114 И К К Н И № И ft К \Ш \h Щ П Щ Л Н Vt И 14 tt 14 14 14 14 !4 14 14 14 24 Jjfj JJJJJJJJJJJJJJJJJJJJJJJJJJJJJJ J Символы datiHMX и проверочные символы(Цканальных Sum символ 8Sum) -Символы управления и ато5ран<ения информации [НпанамныхВит 1 символ 8Sum) Синхрогруппа (гЧ каналвнык бита) - Инверсия  Г Иачалп Влвиа. - ис. 1,21. Формат блока кода EFM одного канального бита Тк составляет относительно длительност одного цифрового бита 47%, т. е. Гк = 0,47Т. Анализ колонки 3 приложения показывает, что для использо вания выбраны лишь такие комбинации единиц и нулей, в кото рых единицы разделены как минимум двумя и как максиму десятью нулями. Таких комбинаций существует всего 277, и и них в таблицу отобрано 256. Тогда Ти.. = ЗГ = 1,41Т, Т„а„с = 1 ITk = 5,187. Преобразование символов в коде EFM производится в соответст ВИИ с порядком, показанным на рис. 1.22. Переходные биты используются для стыковки символов и по. давления низкочастотной составляющей. Рассмотрим, как производится выбор оптимального варианта перехода между символа ми. Использование переходных битов для стыковки символов. На рис. 1.23 показан пример стыковки символов 1 и 32. Если ни на; одном из переходных битов не сформировать импульс перехода, то образуется канальный сигнал (в) с временным интервалом 20 Тк. Такой интервал по правилам кода EFM недопустим. Есл , ввести 1 на первом переходном бите, то образуется сигнал (г) с интервалами ЭГк и ПГк. Такие интервалы правилами разрешены. Разрешенные интервалы образуются и в случае, если разместить 1 на втором переходном бите (д) и третьем (е). Еще один пример стыка символов приведен на рис. 1.24. Здесь за символом 32 следует символ 1. Если переход не выполнить ни на одном из переходных битов, то образуется разрешенный интервал длительностью 97к. Разрешенный интервал ЗГк образует- Выборка: Два символа: 16 разрядов Старшие разряды Символ 1 d,----i Канальные Виты:ХХХ\ С1 после модуляции Clfy XXX Младшие разряды Символ 2 d,----ds CI СП ххк с о г/Аа сования I Прсобраоование символа dj-dg в СимВол С1-Clt соответственно таблицам лре~ образований Вит С1 выходит первым Рис. 1.22. Порядок преобразования символов в коде EFM с введением 3 бит согласования 0 0 0 0 0 0 0 1 Сим бол 3Z 0 0 1 0 0 0 0 0  ) I-L I ЮТк I 11 Тк Рис I 23. Стыковка символов 1 и 32 СЯ таким же образом, если выполнить переход на первом переходном бите (в). Если же выполнить переходы на втором и третьем переходных битах, то образуются неразрешенные временные интервалы 2Гк и Гк (г, д). Приведенные примеры показывают, как переходные биты могут быть использованы для формирования в канальном сигнале разрешенных правилами временных интервалов. Однако кроме формирования разрешенных временных интервалов при стыковке блоков правильный выбор перехода из числа разрешенных вариантов позволяет уменьшить низкочастотные составляющие в канальном сигнале. Рассмотрим пример стыка символов 95 и 158, показанный на рис. 1.25. Введем широко принятый в теории канальных кодов параметр DSV (Digital Sum Value), т. е. цифровую сумму. В любой текущий момент времени цифровая сумма есть алгебраиче- а) 6) в) г) 9) Символ JZ Символ 1 q q о о о о q о 1 0 0 0 0 0 1 о о о q 1 о о о о q о о п П П- г fh--L Нб разрешено Рис. 1.24. Стыковка символов 32 и 1 СимВол as Ствол 15g ,) п-гг ч ,-п-TL  Рис. 1 25. Стыковка символов 95 и 158 екая сумма всех предыдущих канальных бит - единичных - со знаком +, а нулевых - со знаком -. Так, если считать, что в момент начала символа 95 DSy=0, то к его концу DSV станет равным 4. В зависимости от того, какой из вариантов перехода выбирается, дальнейший ход DSV также будет различным. Так, кривая I показывает ход DSV в отсутствие перехода, кривая 2 - при переходе на первом переходном бите, кривая <? - на втором бите, кривая 4 - на третьем бите. Для кривой / к концу символа 158 DSy=+7, для кривой 2 ШУ= + 1, для кривой 3 DSV=-\, а для кривой 4 DSV=--3. Минимальные значения DSV к концу символа 158 при его стыковке с символом 95 обеспечиваются при наличии перехода на первом или втором переходных битах. Может быть выбран любой из них. Для выбора перехода, оптимального с точки зрения разрешенных переходов и минимизации постоянной составляющей, необходимо провести анализ стыка двух символов для определения разрешенных вариантов перехода и из числа разрешенных выбрат тот, который приводит к минимальному значению Определение разрешаемых вариантов перехода. На рис. 1.2 воспроизведены канальный символ 47 из колонки 3 приложения, соответствующая ему временная диаграмма (б), временная диаграмма сигнала на выходе счетного триггера (в), на вход которого подается предыдущий сигнал, и вариация DSV в течение символа (г). Введем обозначения, используемые в дальнейшем: BW - число нулей в сигнале CWI в начале символа, пока зывающее длительность имеющего нулевой уровень первого ин тервала сигнала CW. Если символ начинается с единицы, т 54 1 2 3 4 5 6 7 8 ... 22 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|